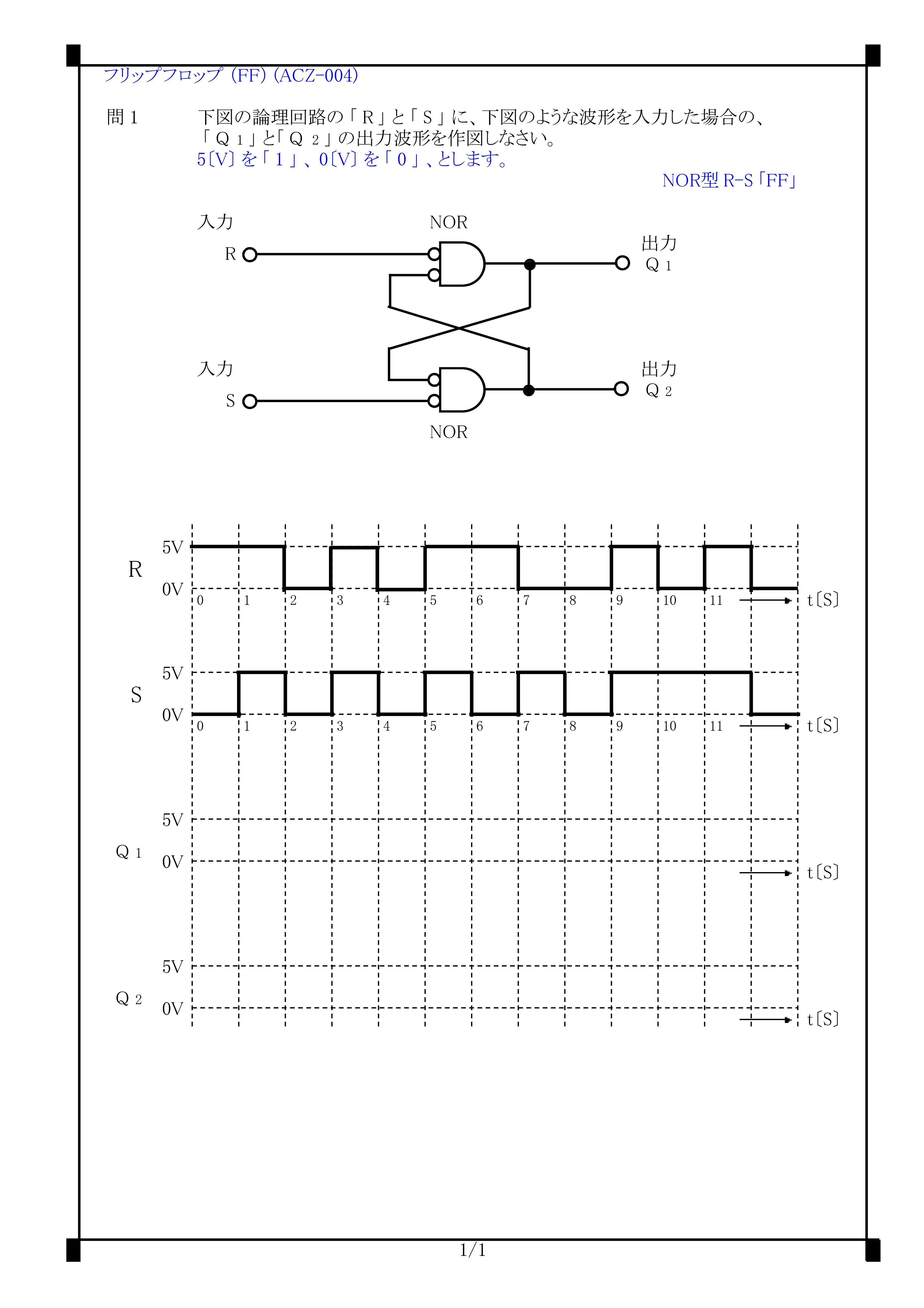

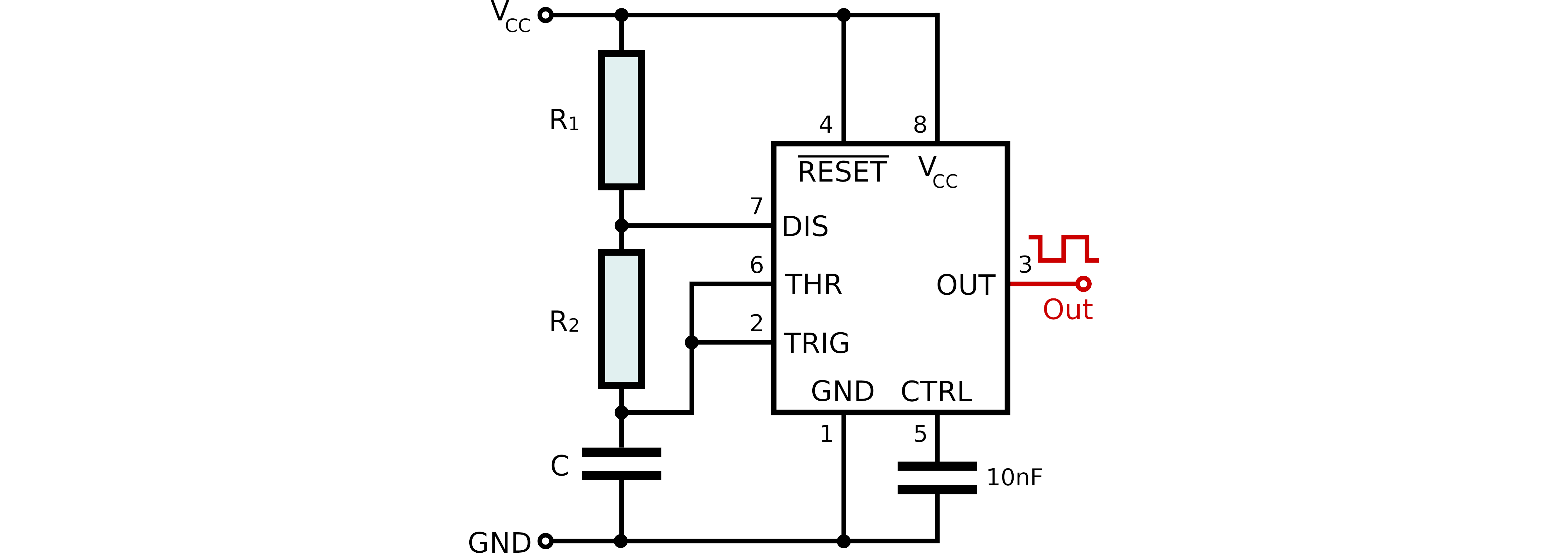

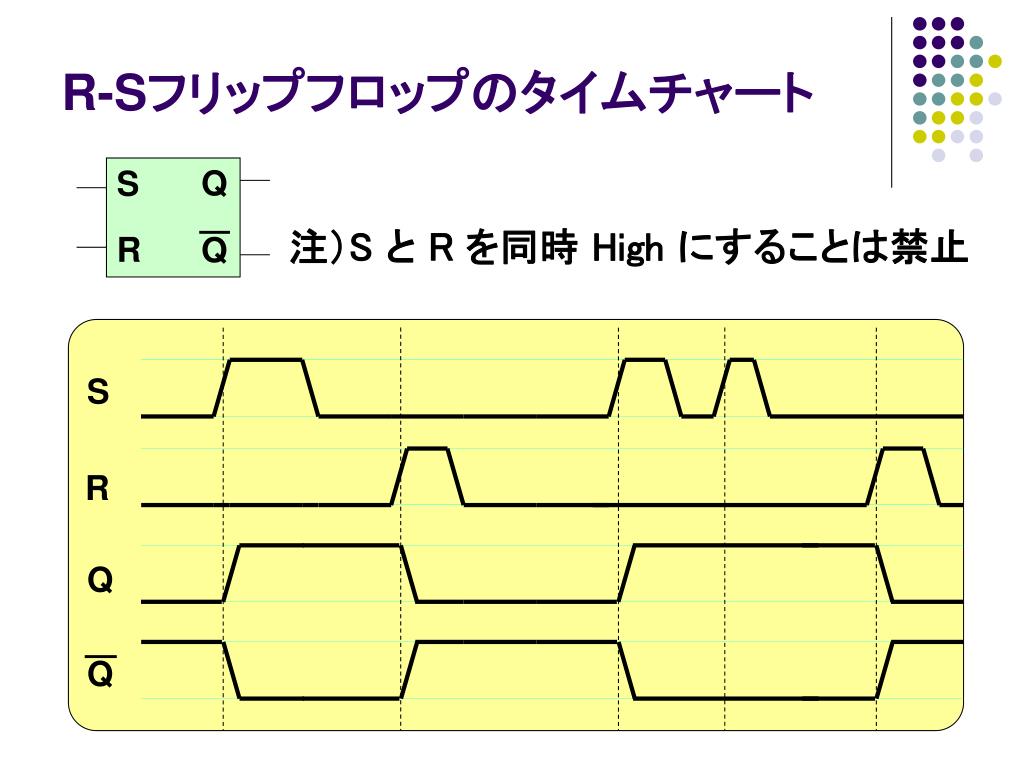

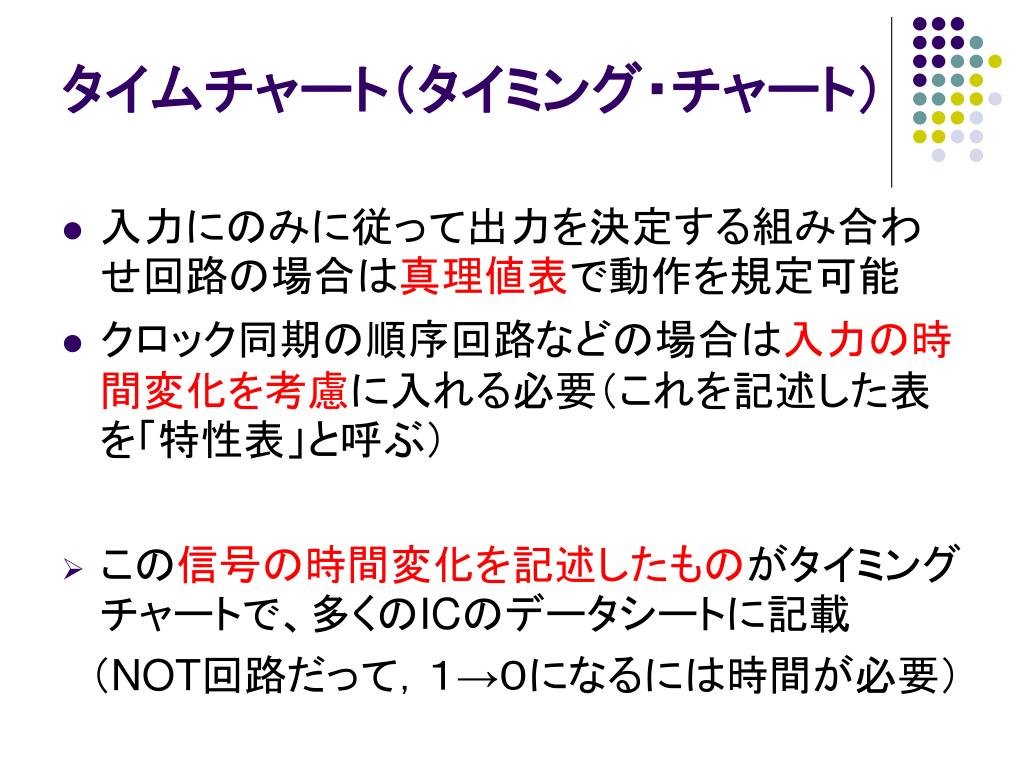

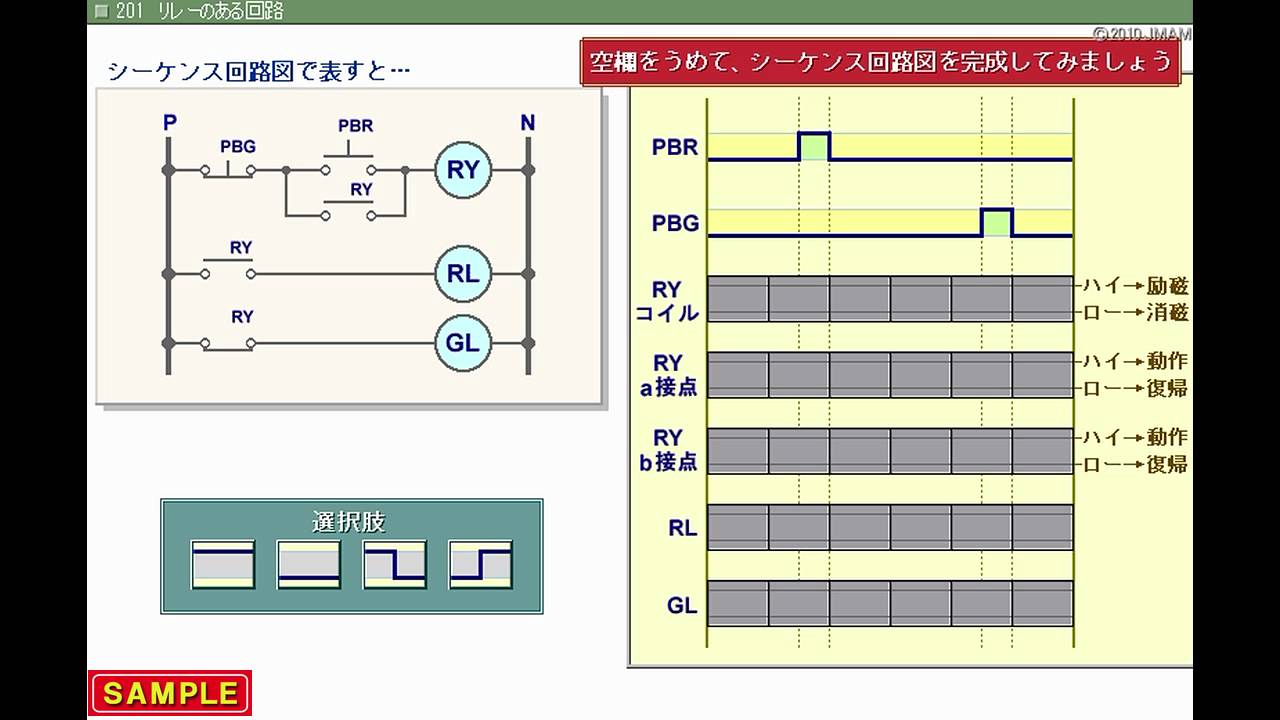

フリップフロッ プ タイムチャートは以下のようになります。 x0がonして faで重要な要素は自動運転です。faの自動運転は運転ストーリーをシーケンスという順序でつくりますが、どのように、つくる論理回路 Rsフリップフロップ回路 東芝デバイス ストレージ株式会社 日本 問題13 Sr Ffのタイムチャート 完全マスター 電子回路ドリル Ii 15 Monoist Jkフリップフロップ 石丸技術士事務所 ディジタル1 はじめに 本章では、順序回路の基本であるフリップフロップについて学習します。 「論理回路1」で学んだ「組合せ回路」にはなかった、時間の要素が加わります。 タイムチャート等、最初は慣れない項目があるかもしれませんが、組合せ回路の基本を復習すれば、十分理解できると思います。 11 順序回路とは 順序回路とは、その時点の入力のみならず、過去

リレーだけでdffを作ってみる Qiita

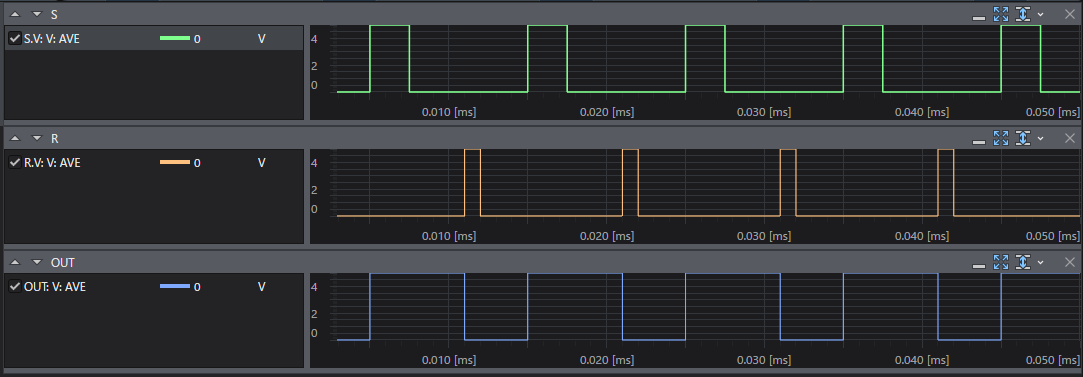

Rs フリップフロッ プ タイム チャート

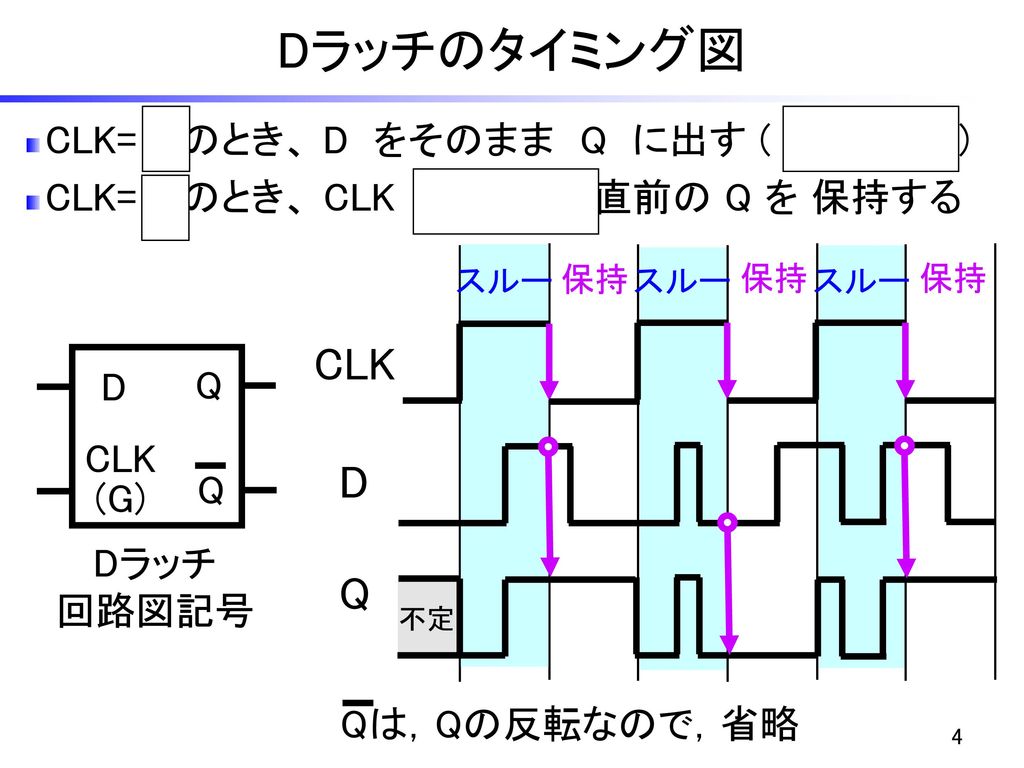

Rs フリップフロッ プ タイム チャート-最初に、RSTフリップフロップを使った実現方法を示す。 次の回路では、入力信号Dの値を変更しても、それが出力に伝わるのは、入力信号Tの値が1のときである。 現時刻の入力信号 D, T および出力信号 Q, Q の値をそれぞれ i0, t0 および o0, o1 で表す。» フリップフロップ,カウンタ » タイミングチャート,クロック » 有限状態マシン

フリップフロップとは コンピュータの人気 最新記事を集めました はてな

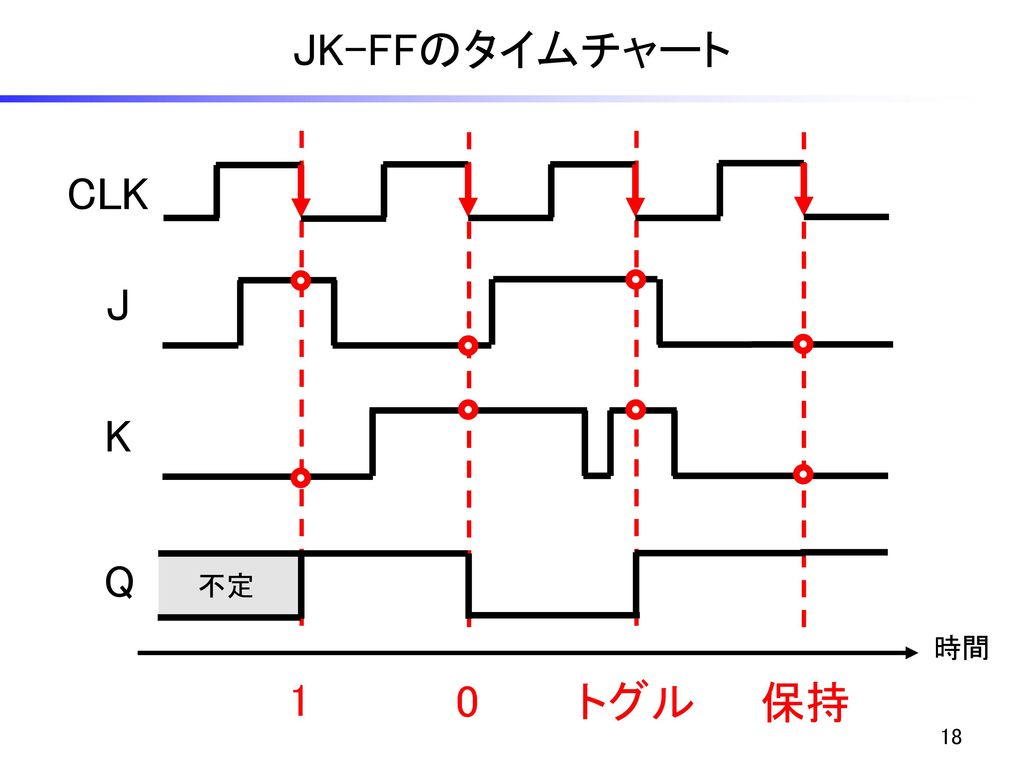

· 問題14 jkffのタイムチャート 問題13 srffのタイムチャート 問題12 フリップフロップの動作;記憶回路(フリップフロップ) コンピュータの仕組み 私たちが何らかの計算問題を解こうとする時、途中の計算結果を紙にメモしたりすることがあると思います。 コンピュータの中にも計算結果やその他いろいろな信号を保存しておくための記憶回路が存在します。 1本の信号線があると仮定して、この信号線の状態がある瞬間に「1」であったのかもしくは「0Jk フリップフロッ プ 特性 表 0c4y8 Ddns Info;

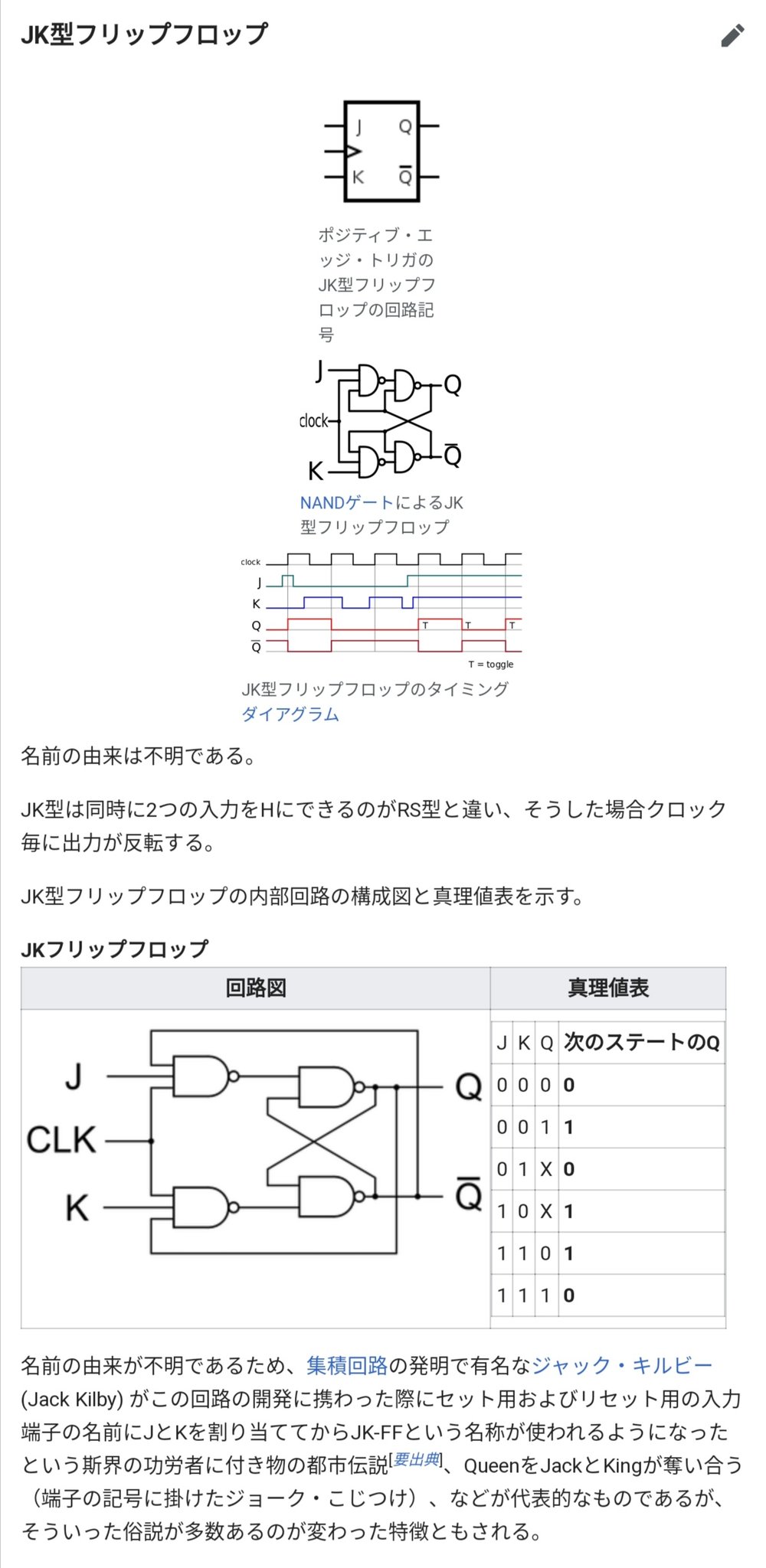

また、rsff(rs フリップフロップ)、tff(tフリップフロップ)など、他のタイプのフリップフロップと同じ動作をさせることができる。このような 多機能性から、jkffは万能 ffとも形容される。 jkffの基本 動作は、次の4パターンである。 リセットクロック付きrs フリップフロップは, ・s =1,r =0 でクロックc が( )とき,q =( ),q =( )となり, sl() 0 rl() 1 ql(9) ql() 端子(ランプ) 図8 r−s フリップフロップのタイムチャート 図9 クロック端子付きr−s フリップフロップの回路図 入力(スイッチ)(ランプ) 出力(ランプ) ss l()()例題103:非同期式5進カウンタの真理値表とタイムチャートから, 動作を解析し回路を構成せよ。(clr回路なし,jkff3段)1/2 ffa ck1 ~ck4 のck 立下がりでトグル動作 この期間 ゆえ,ka=1ならffaはトグル動作 ffb qbはqaの立下がりでトグル動作

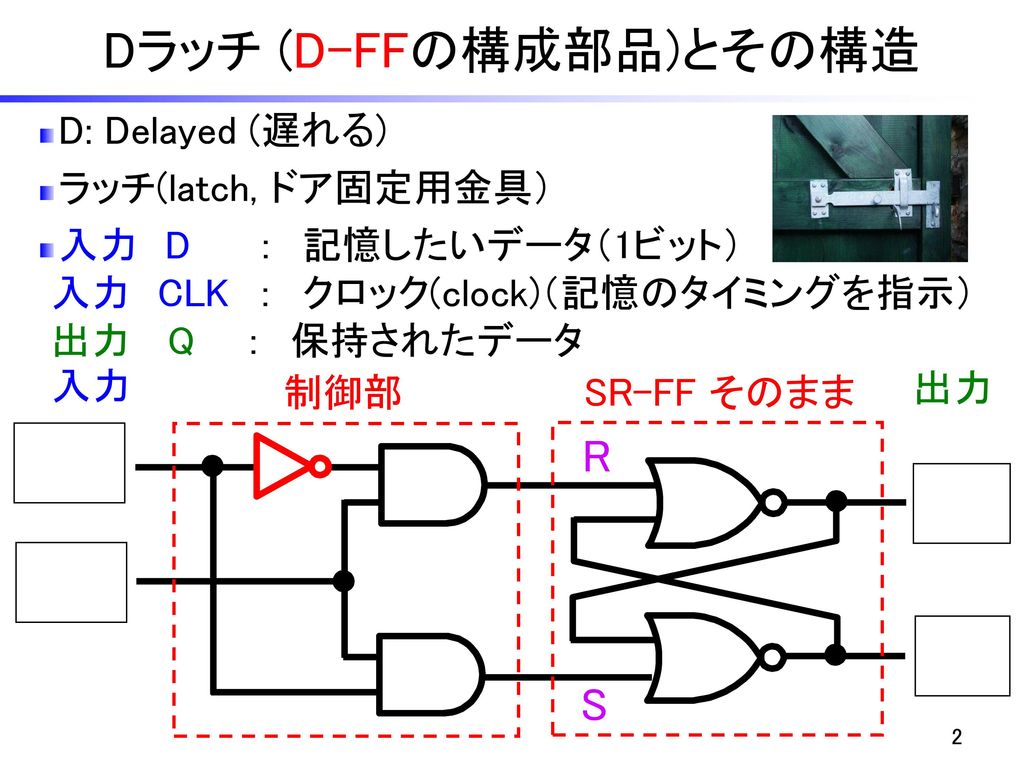

R S 0 0 D D D Holds D when clock goes low Holds D when clock goes low エッジトリガー型フリップフロップ 状態変化をクロックの上がり エッジか下りエッジのタイミン グで起こすようにしたFF。 使い易いがダイナミックな動 作になるので使用には注意 が必要。(7474)TOP 知恵袋 37 基本順序回路:フリップフロップ 37 基本順序回路:フリップフロップ フリップフロップ(FlipFlop)は、1ビットの情報を保持(記憶)できる論理回路です。相補的に動作する2つのスイッチ素子から構成されており、入力が無い限り元の状態を保持します。 · rsffを用いてチャタリングを防止するスイッチを作るにはどうしたらいいでしょうか? 回路図や分かりやすい説明をお願いします。 ご承知のようにチャッタリングは、図のように2→1にスイッチを切り替えたとき、しばらくバタ

リレーだけでdffを作ってみる Qiita

パワーアップされたwbsガントチャート For Jiraでプロジェクト管理をレベルアップ 割引キャンペーン リックソフト

フリップフロップ Wikipedia 順序回路、フリップフロップ Renesas;Jkフリップフロップ2つで構成した次の回路の動作を検討する. q 0 は,クロック入力のたびに0, 1 を繰り返す ;そのタイムチャートを以下に示します。 このカウンタの出力は、(0→1→2)というように、1クロックごとにカウントアップします。 なお、各フリップフロップのqを出力をすれば、(7→6→5)というように、 カウントダウンする カウンタとなります。

Acz 004 Rsフリップフロップの動作 Rs Ff Nand型rsフリップフロップ Nor型rsフリップフロップ フリップフロップ の入出力波形 順序回路 記憶回路 0アクティブ 1アクティブ Ff 電気の問題集研究所 Dmk Note

19 0076号 デューティ比検出回路及びデューティ比の検出方法 Astamuse

J 1 =k 1 =q 0 であるから, q 0 =0の状態でクロック信号が入力すると, q 1 の状態は変化しない.(保持動作) ;2 (6) rsフリップ・フロップ1 (基本の回路、基本の動作、状態遷移表、状態遷移図、特性表、特性方程式、タイミングチャート、禁止入力) 2 (7) rsフリップ・フロップ2 (クロックの導入、禁止入力の改善 (セット優先、リセット優先)、マスタースレーブrsff) 2フリップ・フロップ 回路2 「フリップ・フロップ回路1」では、スイッチの接 触不良(チャタリング)がある場合に「リレーS」 が1回のスイッチ操作で数回動くことになる。 結果、フリップ・フロップの状態がどちらか分か らない。 上記のことがある為、機械の制御等には、押 しボタン

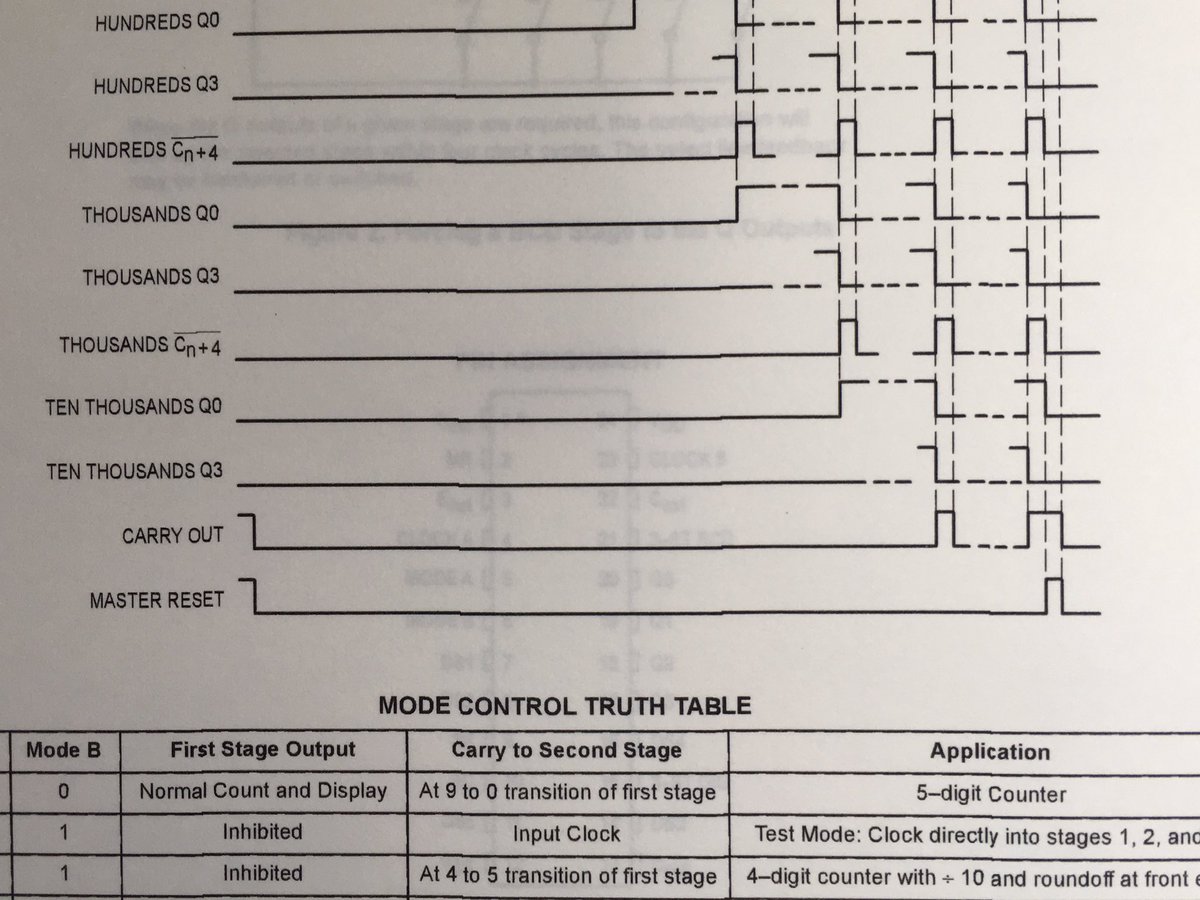

みかんとひよどり C Mos 4000シリーズの5桁カウンター4534の不思議な仕様 カウンターのオーバーフロー Carry Out 信号が何故かオーバーフローした時だけでなくカウンターリセット時にも出力される オーバーフローした事をledで表示しようとして Rs Ffで

フリップフロップとは コンピュータの人気 最新記事を集めました はてな

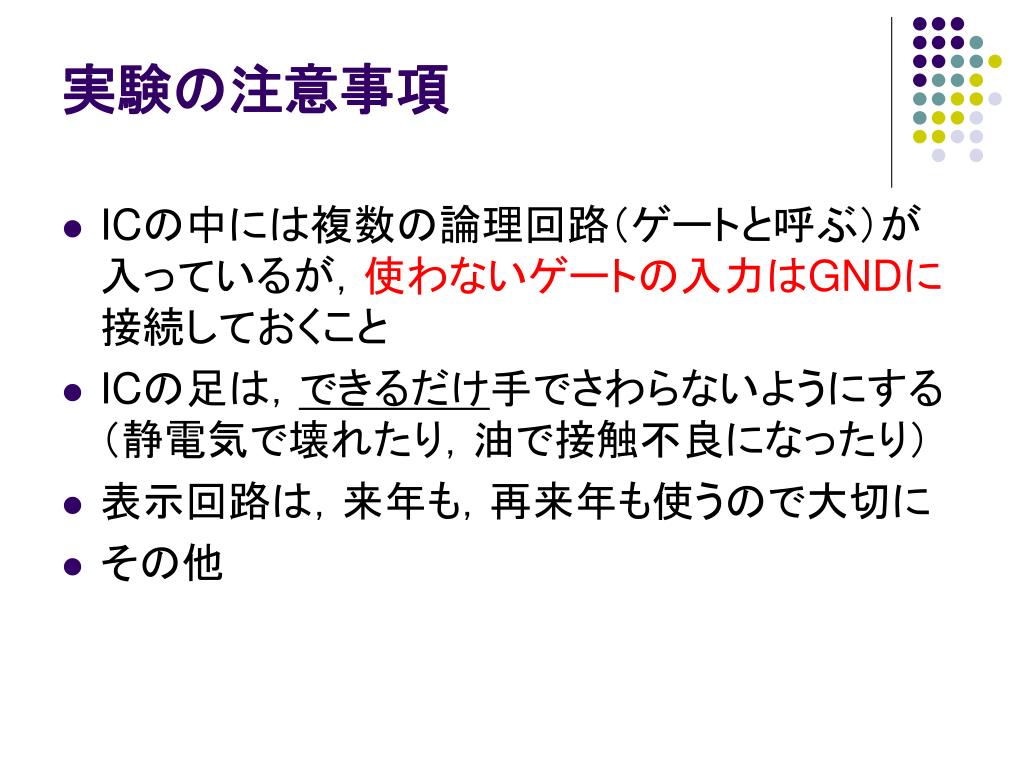

Rsフリップフロップ(図11,図12)は割り込み(インタ ラプト)の受け付けなどに使用されます.rsフリップフロッ プが取り扱う信号は非同期となるので,静的タイミング解析 をともなう論理合成の際には注意が必要です.Rsフリップフロップ回路とjkフリップフロッ プ回路について予習してください。 科: 必須・選択 開講時期 単位 時間/週 内線電話番号 No ① ② ③ ④ ⑤ ⑥ ⑦ ⑧ ⑨ ⑩ 試験 小テスト レポート 制作物 成果発表 その他 合計 60 30 10 100 10Q 0 =1の状態でクロック信号が入力すると, q 1 は状態を反転する.(反転動作

リレーだけでdffを作ってみる Qiita

Degc9sh I541 M

フリップフロッ プ 自己 保持 回路 これ フリップフロップは複数で使うのが一般的 プロセス文を記述するとき,一般に1個のフリップフロッ プだけを記述するために用いることはまれです.たいていの場 合,複数のフリップフロップからなる回路となりR s この回路はt = 0 のとき, s = 1, r = 0 でq = 1 s = 0, r = 1 でq = 0 srt ffは外部からの制御信号で初期状態が決定できるので計数回路として使用される (v) t フリップフロップー計数回路ー 35 t ff は2 個の信号が入力されると元の状態に戻る回路である. タイミング3 図3:フリップフロップのタイミングチャート 4 タイプのフリップフロップを挙げたが,設計の容易さから一般的にd フリップフロッ jk フリップフロッ プ 特性 表 jkフリップフロップの動作特性 q=0の状態で,j=0を入力すると,q=0を保持する q=0の状態で,j=1を入力すると,q=1に遷移する q

電気回路 Hdl 非同期信号を扱うための危ういverilogライブラリ 武内 筑波大

ttlでcpuを作ろう

フリップフロッ プ 回路 と はフリップフロップとカウンタ 公益社団法人 日本電気技術者協会 論理回路srフリップフロップ 画像のような回路にタイム R S Tフリップフロップ フリップフロップ 問題14 Jk Ffのタイムチャート Monoist ディジタル回路の基礎 2 原理 宮崎技術研究所の技術フリップフロッ プ 回路 図 dipjp;

Fs Micro Corporation

Fs Micro Corporation

5 フリップフロップ ¶ フリップフロップは 1bit のデータを記憶する回路である。 入力信号により1または0を記憶し、値の変更を指示する信号が 入力されるまでは、最後に記憶した値を保持し出力し続ける。 フリップフロップを多数用意することで、コンピュータの記憶装置を実現できる。 以下では値を保持、記憶する基本の回路を最初に示し、その後その機能を論理 回路 フリップフロッ プ 最も人気のある! Rs フリップフロッ プ タイム チャート NO1 ディジタル回路技術の応用 技術者教育のコガク;フリップ・フロップ リレー回路 TSYSTEM 1回押すとON もう一度押すとOFFという回路を ラッチリレーを使っ 電子工作 回路編10トランジスタ2石のRSフリップ フリップフロッ プ 回路 図 T フリップフロッ プ>tff 回路図

Ppt ディジタル回路実験1 2 Powerpoint Presentation Free Download Id

公開特許公報

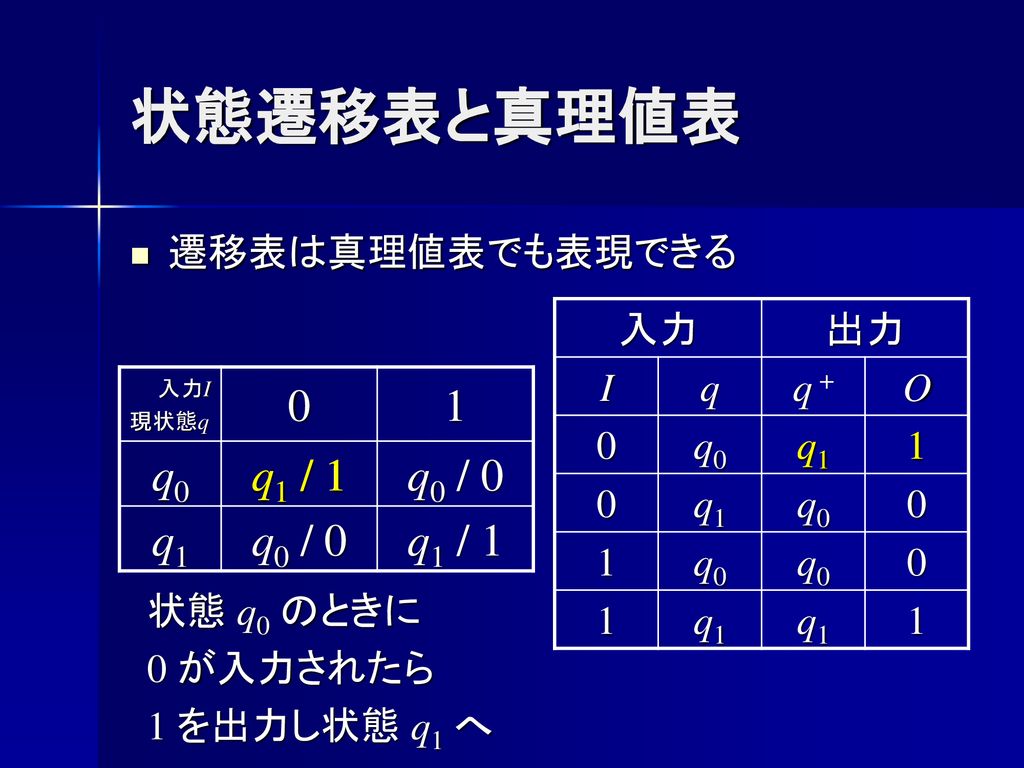

RSフリップフロップ イッツコム 「Dフリップフロップ」の解説(1) しなぷすのハード製作記 コンピュータ工学 講義プリント(5 月15 日 BiGNET;RSフリップフロッ 同期式回路では、パワオンリセットなどの、回路を初期化する目的以外には 35 Rs フリップフロッ プ タイム チャート 論理回路 問題13 Sr Ffのタイムチャート Monoist 問題14 Jk Ffのタイムチャート Monoist · うさぎでもわかる計算機システム Part08 フリップフロップ(D・T・RS・JK)・クロックとタイミングチャートの書き方 こんにちは、ももやまです。 今回は順序回路であるフリップフロップについての説明をしたいとおもいます。 論理回路の基礎であるAND回路・OR回路が登場してくるので、基本的なAND・OR回路などの理解がまだできてない人はこちらの記事で

論理回路 フリップフロップの動作原理 Youtube

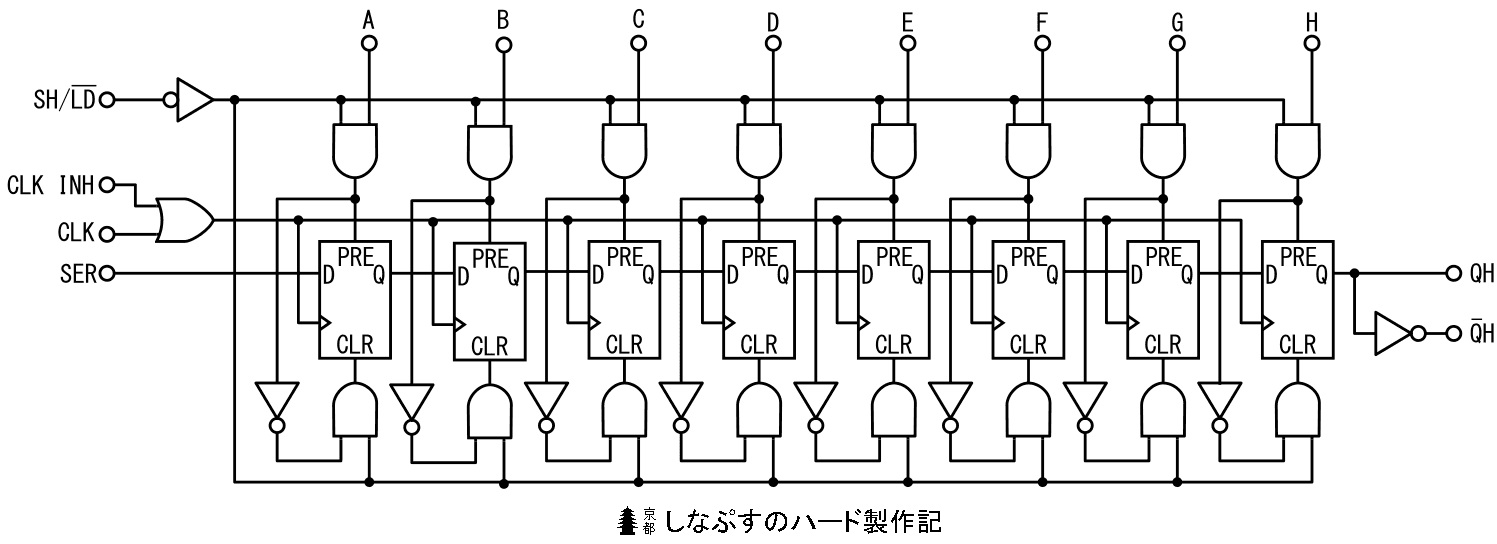

09 号 シリアルパラレル変換回路の設計方法およびシリアルパラレル変換回路 Astamuse

演習 各フリップフロップのタイムチャートのおける出力波形がどうなるか予習して,全て フリップフロップ(rs,jkフリップフロ ップ) フリップフロップ(t,dフリップフロッ プ) 順序論理回路設計方法の基礎 順序論理回路の具体例(カウンタ,レジT型フリップフロ ップ510,5,530のロック解除確認後、1ビ ットカウンタ4へ有効エッジが印加される。その有効エ ッジの印加タイミングを調整するのが、タイミング制御 回路14である。フリップフロップ・双安定回路 1 (英 flipflop, bistable circuit )は、二進法の基本である1ビットの情報を一時的に'0'または'1'の状態として保持する(記憶する)ことができる論理回路で、順序回路の基本要素である。 フリップフロップ、マスタースレーブ型JK フリップフロッ プの動作をタイミングチャートを示し解説する。 中間試験 組み合わせ論理回路の設計

フリップフロップ回路 Youtube

74hc595 の解説 しなぷすのハード製作記

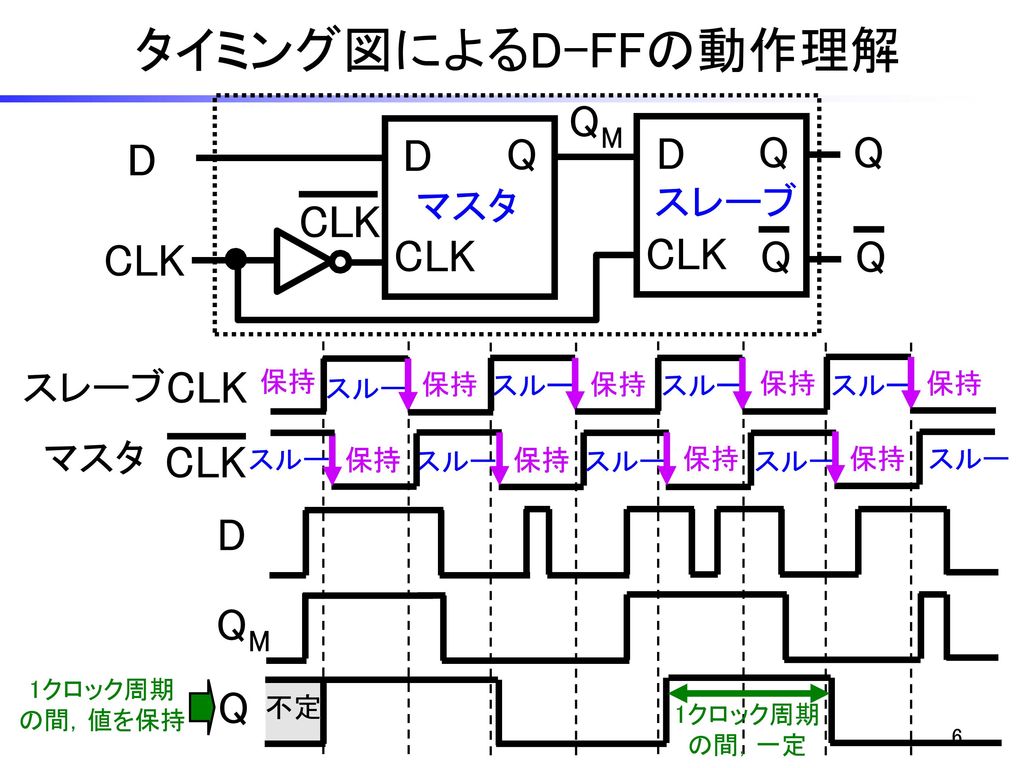

第10回 Dフリップフロップ ディジタル回路で特に重要な D Ff 仕組みを理解する タイミング図を読み書きできるようにする 瀬戸 Ppt Download

Ppt ディジタル回路実験1 2 Powerpoint Presentation Free Download Id

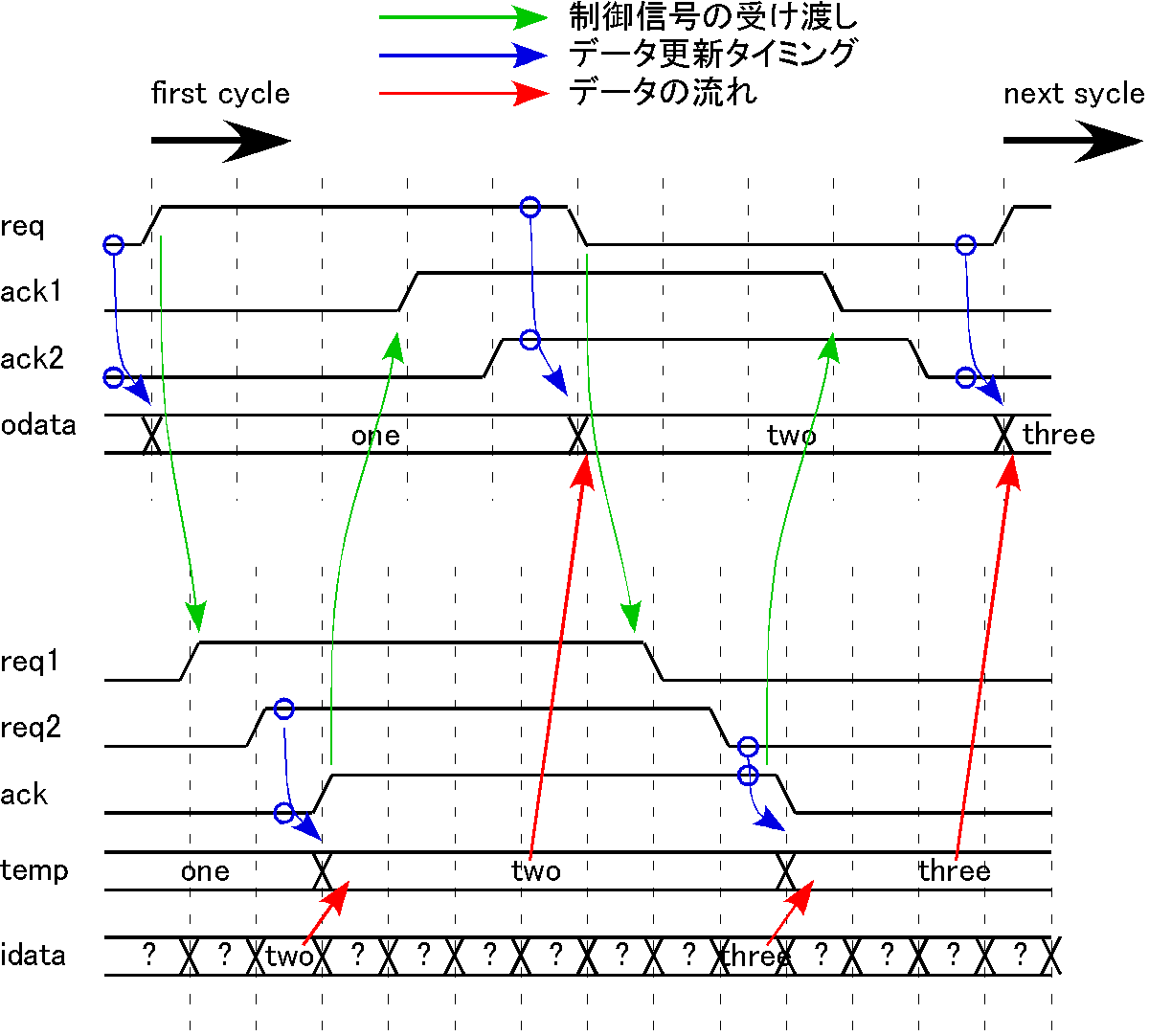

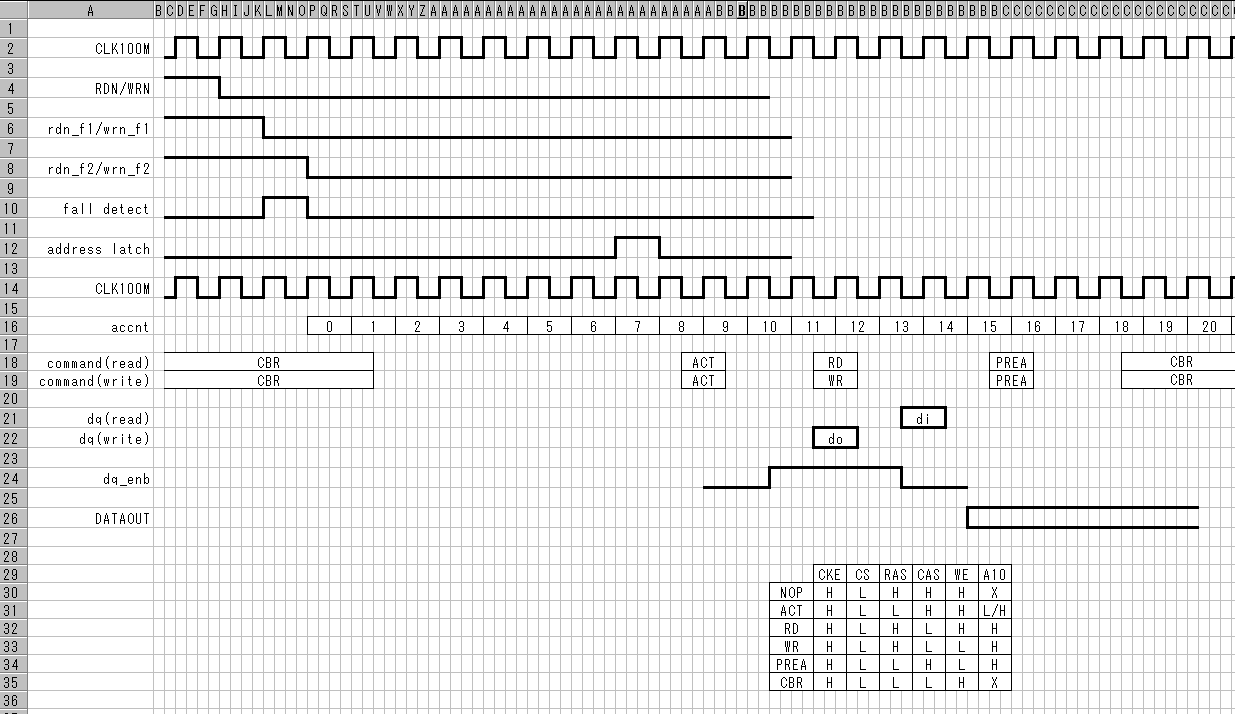

Membuf

09 号 シリアルパラレル変換回路の設計方法およびシリアルパラレル変換回路 Astamuse

第10回 Dフリップフロップ ディジタル回路で特に重要な D Ff 仕組みを理解する タイミング図を読み書きできるようにする 瀬戸 Ppt Download

74hc165 の解説 しなぷすのハード製作記

07 号 ダイナミック型フリップフロップ回路 Astamuse

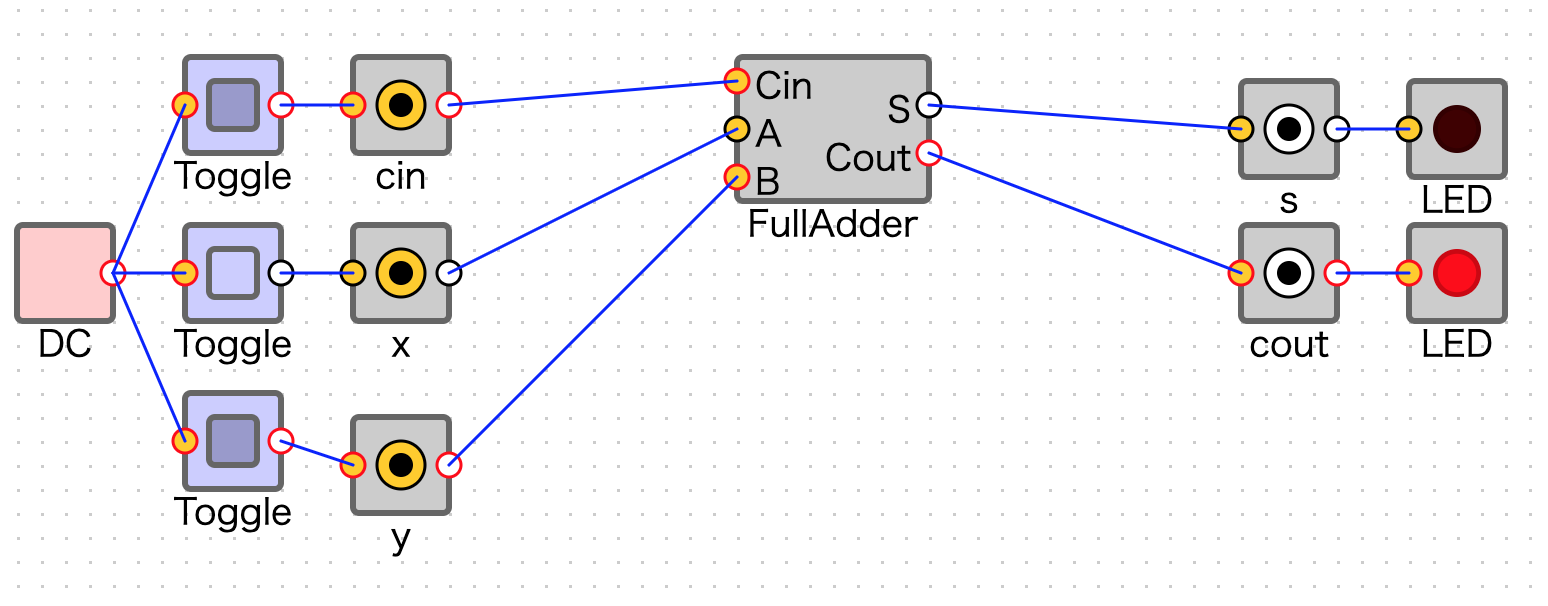

7 2 課題 論理回路シミュレータ

第10回 Dフリップフロップ ディジタル回路で特に重要な D Ff 仕組みを理解する タイミング図を読み書きできるようにする 瀬戸 Ppt Download

リレーシーケンスのオルタネート フリップフロップ 回路 基礎からわかる電気技術者の知識と資格

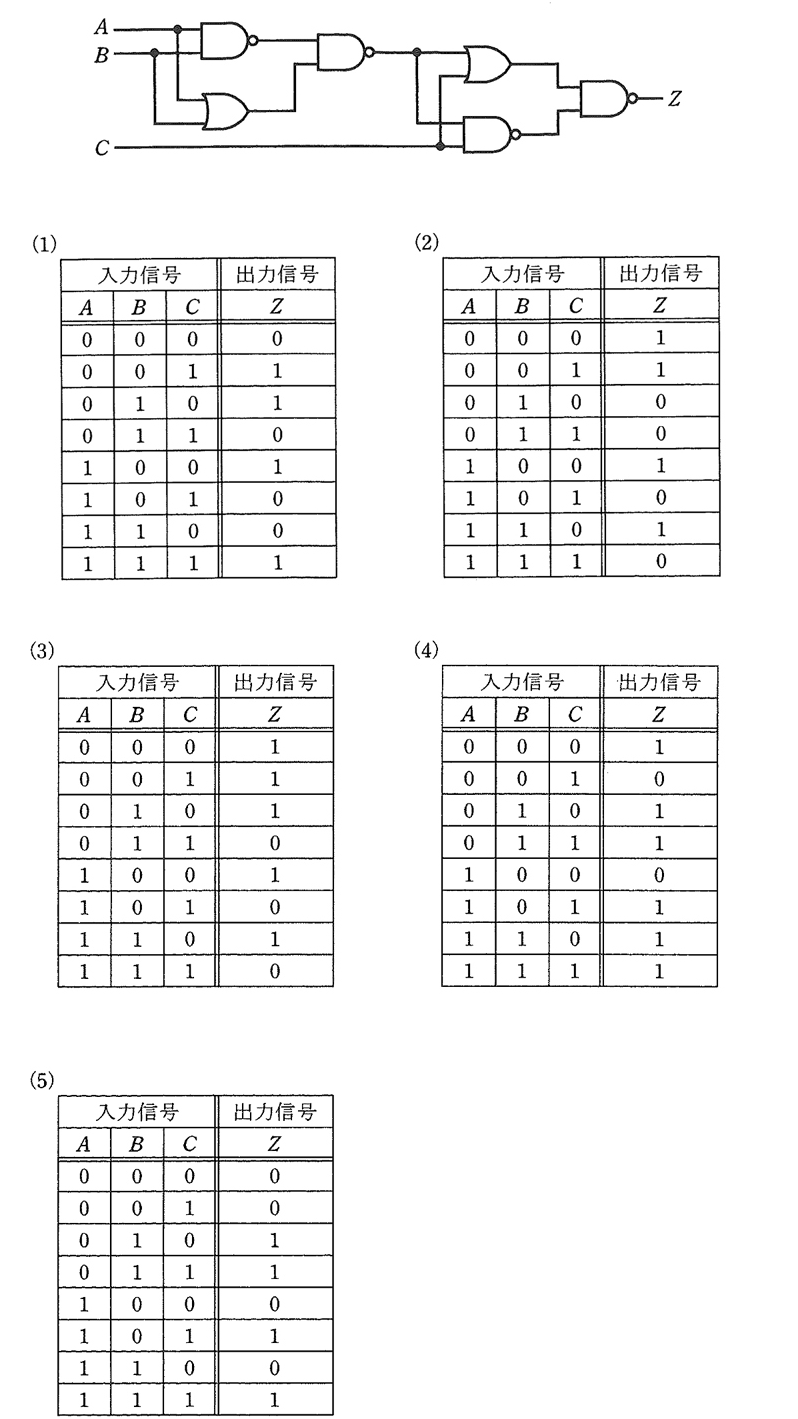

7 練習問題の答 Digital Electronic Circuits 1 0 ドキュメント

日本財団図書館 電子図書館 船舶電気装備技術講座 gmdss 基礎理論編

Ppt ディジタル回路実験1 2 Powerpoint Presentation Free Download Id

Membuf

トコトンやさしいデジタル回路の本 電子回路 回路設計 デジタル回路 ビジネス 電気 電子 本 雑誌 日刊工業新聞

ttlでcpuを作ろう

Eclによるdフリップフロップ さしあたって

ヤフオク ディジタル回路のシステム設計 基礎 問題解決の

論理回路とn進数 基礎からわかる電気技術者の知識と資格

07 号 ダイナミック型フリップフロップ回路 Astamuse

第10回 Dフリップフロップ ディジタル回路で特に重要な D Ff 仕組みを理解する タイミング図を読み書きできるようにする 瀬戸 Ppt Download

Jmam Eラーニング ライブラリ シーケンス制御の基礎コース タイムチ Youtube

メルカリ ディジタル回路 新インターユニバーシティ コンピュータ It 9 中古や未使用のフリマ

桃杖海姫 アナクロリマスター版 失礼いたしました Jk型フリップフロップというのをどこかで使いたかっただけの冗談ですのでお気になさらずに

19年05月 電子工作を楽しもう

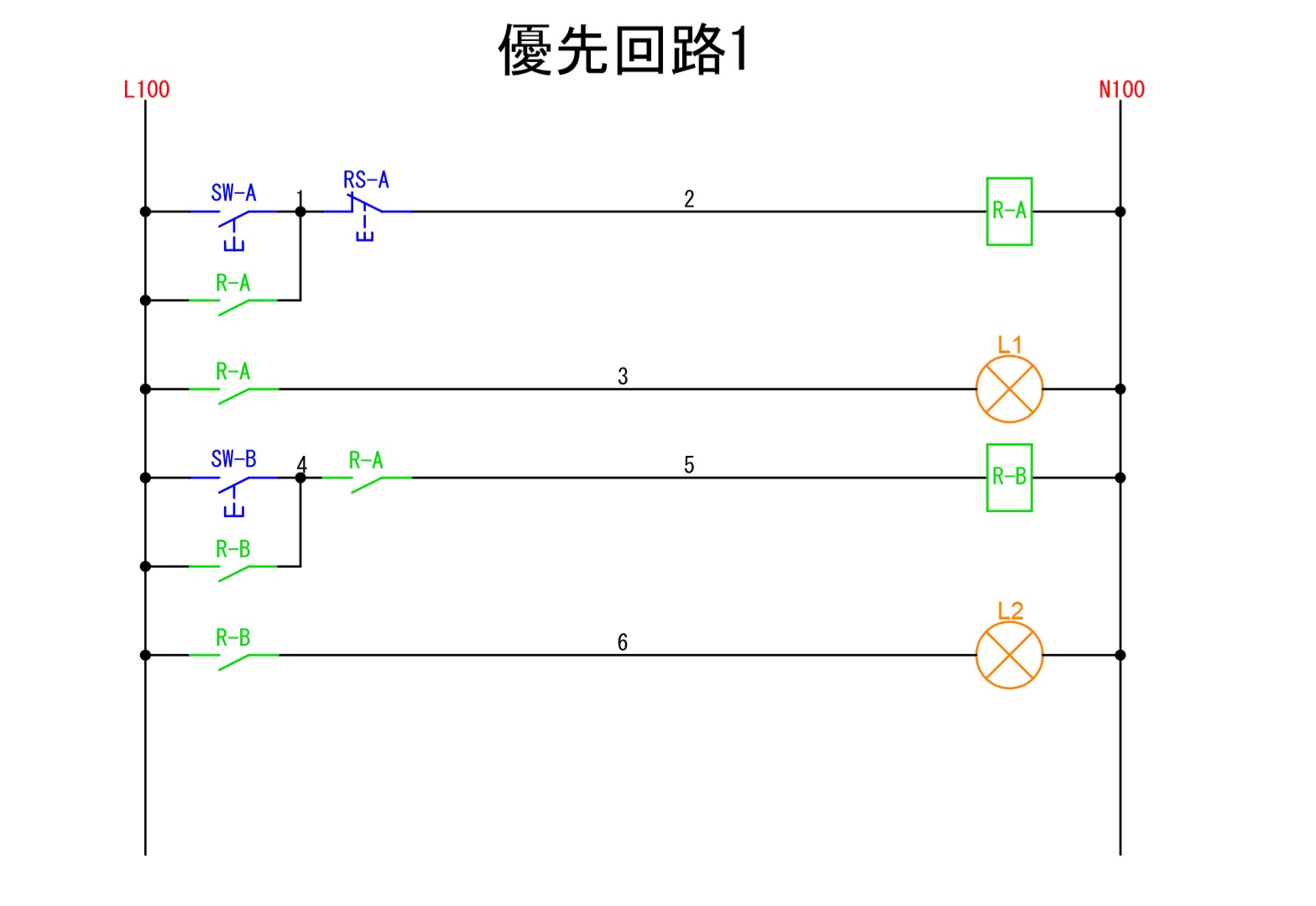

一般的な回路 シーケンスの常用回路 やさしく解説する電気 受電から制御まで

29 p6つくろうブログ

D Testshare

フリップフロップ Scideam Help Center

Pdf Free Download

論理回路 第9回 フリップフロップ 38号館4階n 411 内線 Ppt Download

ttlでcpuを作ろう

フリップフロップ Wikipedia

0 件のコメント:

コメントを投稿